1.IO默认状态

上电期间,所有GPIO都处于高阻抗模拟状态,并且禁用了输入缓冲器。 在运行期间,可以通过写入关联的寄存器来配置GPIO。 请注意,在通电期间,支持调试访问端口(DAP)连接(SWD线)的引脚始终作为SWD线启用。 DAP连接不提供上拉或下拉电阻;因此,如果悬空,可能会产生一些撬棍电流。只有在设备启动并开始执行代码后,才可以通过HSIOM禁用或重新配置DAP连接以用于通用。

2.输入缓冲器

模拟输入通常禁用输入缓冲器,数字输入通常使能输入缓冲器。

虽然最好使用模拟引脚禁用输入缓冲器,但是如果需要同时使用模拟和数字输入功能,也可以启用输入缓冲器。

原文:

高阻抗模式是推荐用于模拟和数字输入的标准高阻抗(High-Z)状态。对于数字信号,使能输入缓冲器; 对于模拟信号,通常禁用输入缓冲器,以减少低功耗设计中的撬杠电流和泄漏。 为了获得最低的器件电流,必须在禁用输入缓冲器的情况下将未使用的GPIO配置为高阻抗驱动模式。 禁用输入缓冲器的高阻抗驱动模式也是默认的引脚复位状态。

3.IO模式

4.关于压摆率 Slew Rate

仅增强型I / O端口将支持压摆率控制。 对于标准端口,压摆率可以使用驱动强度来控制。 有关具有增强功能的I / O端口,请参考器件数据手册。

5.IO的驱动能力应如何选择

Drive strength的描述见TRM,主要考虑驱动能力和EMI和串扰之间的平衡。一般情况选择默认模式即可,除非遇到EMI相关问题。

Some GPIO pins have fast and slow output slew rate options for the strong drivers configured using the SLOW bit of the port output configuration register (GPIO_PRTx_CFG_OUT). By default, this bit is cleared and the port works in fast slew mode. This bit can be set if a slow slew rate is required. Slower slew rate results in reduced EMI and crosstalk and are recommended for low-frequency signals or signals without strict timing constraints.

某些GPIO引脚具有使用端口输出配置寄存器(GPIO_PRTx_CFG_OUT)的SLOW位配置的强驱动器的快速和慢速输出摆率选项。 默认情况下,该位清零,并且端口在快速转换模式下工作。 如果需要较低的压摆率,则可以将该位置1。 较低的压摆率可降低EMI和串扰,建议将其用于低频信号或无严格时序限制的信号。

需要注意TRM所述的one-eighth strength在TVII中是不支持的,后续会更新手册。

6.外部中断

所有端口引脚都具有产生中断的能力。

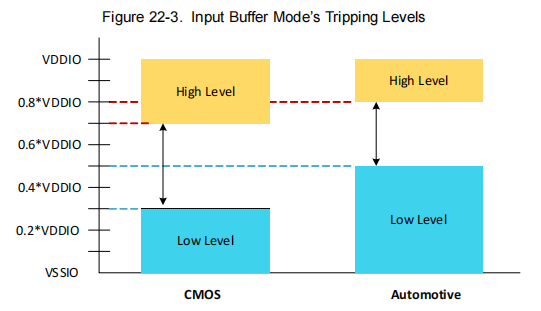

7.输入阈值

默认配置均为CMOS模式:

评论区